# HIGH SPEED AND LOW POWER FLASH ADC DESIGN

PRAJAKTA RAVINDRA MORE

Department of Electronics and Communication, Sandip Institute of Research and Technology Nasik, India prajktamorerrr@gmail.com

#### PROF. DR. G.M.PHADE

Department of Electronics and Communication, Sandip Institute of Research and Technology Nasik, India

#### **ABSTRACT:**

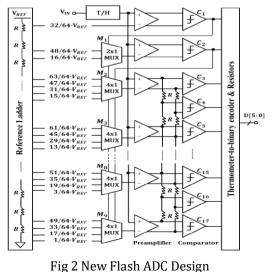

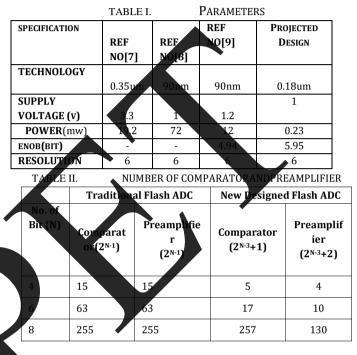

The Analog to Digital converters play an imperative role in today's electronic systems world. Current applications need High Speed and Low Power ADC. Flash ADC is most prevalent not only for its highest transformation rate but also for its use in other ADC types and its varied applications. Traditional N-bit flash ADC necessitates 2<sup>N-1</sup> comparator and same number of preamplifier. if we use multiplexer to design FLASH ADC number of Comparator and Preamplifier get reduced also use of mux in Thermometer to binary code encoder will reduce delay which will ultimately reduce overall power consumption, area and will rise the speed of operation. KEYWORDS: Flash ADC, Multiplexer, Pramplifier, Comparator Thermometer To Binary code Encoder.

## I. INTRODUCTION:

Flash ADC's, also known such as parallel ADCs, the firmest in converting an analog signal to a digital signal. Which are used in various applications in which higher speed and resolution required such as wireless communications and digital audio and video, Radar Processing ,High Density Disk dr ive, numerous types of architectures, with distinctive characteristics and different limitations 1. One of the design which is used onverting co ntinuous time ignal to digital signal is Flash ADC 🗋 changing *s*

# II. EASE OF

A. TRADITIONAL FLASH ADC:

Fig 1 Traditional Flash ADC

The Resistor ladder setup generates the reference voltages for the every Comparator. The reference voltage for each Comparator is1 LSB less than the locus voltage for

the Comparator promptly upstairs it. When the input voltage (positive terminal) is superiorthan the locus voltage (negative voltage) of Comparator it produces a "1", otherwise, the Comparator productivity is "0". If the analog input is in among  $\mathcal{N}_{\mathcal{M}}$  and  $\mathcal{N}_{\mathcal{M}}$  , then the Comparators X1 "1"s and all the left over Comparators throughX4 food produce "0"s. the Comparators will generate a Thermometer code of an input signal. This code will then encode into a Binary form by T To B Converter. They are typically stumpy Gain since at great Frequencies it is not ether wide Bandwidth and high Gain. The to obtain tog roblem with the Traditional flash architecture is mai nber of comparators surges diacritically with that the n he number of bits. Due to the huge number of nparators the number of bits is usually inadequate, nce the area of chip and consumed power would be too lky for upper determinations. The big number of omparators sources the large input capacitance [3]. To drive such a large input capacitance, preamplifiers are eeded but preamplifiers consume extra power, so it is nperative to reduce the quantity of input preamplifier pairs [4]. The interpolation techniques are used to lessen number of preamplifiers, but the quantity of comparators still remnants at  $2^{N}$  - 1 for an N-bit ADC. On the other hand, the future ADC architecture using multiplexers needs less quantity of comparator and preamplifier too.

# **B. PROJECTED FLSH ADC DESIGN:**

Fig 3 Preamplifier and laten Comparator[5] The first comparator, C1 compares the sampled and amplified input signal with the central reference level,

32/64 VREF1.It chooses SB of the digital output and the MSB becomes the switch signal for the MUXs M1 – M9. The subsequent comparator, C2, does the same but it s reference signal is either 16/64.VRER 2 or 48/64·V roughthe (2x1)-MUX, which is determined by the switch signal from the production of the first comparator. And then these twoMSBs, the outputs of the first and subsequent comparators, decide thereference voltages for the left over comparators, C<sub>3</sub> to C17through (4x1)-MUXs.Thequantity ofpreamplifiersreduce by (4x1)-MUXs, the interpolation techniqueusing two resistors is applied. The outputs of the left overcomparators are set into appropriate values and then alldigital bits are output at the matching time. Projected design needs only  $2^{(N-3)} + 2$  preamplifiers and  $2^{(N-2)}$  +1 comparators. The quantity of comparators needed for the projected ADC can be calculated as below. the first comparator (C1) picks the MSB with the central referencelevel, and due tothe use of the subsequent comparator (C2) with the 1/4·VREF and 3/4·VREF the quantity of comparators apart since these two ( $C_1$  and  $C_2$ )

can be abridged by half, resulting in the total count of comparators of  $2^{(N-2)}$  + 1. The number of preamplifiers required is also abridged from  $2^{(N-2)}$  + 1 to  $2^{(N-3)}$  + 2 since the interpolate by two technique used. Abbreviations and Acronyms

LSB-Least Significant Bit, MSB – Most significant Bit

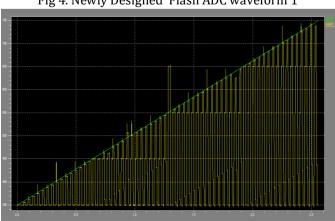

# C. TABLES AND FIGURE OF RESULT:

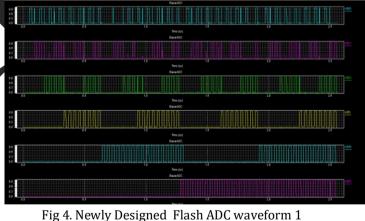

Fig 5. Newly Designed Flash ADC waveform 2

## ACKNOWLEDGMENT:

Prof. Dr. G. M. Phade mam and Mr. Pravin Dhulekar Sir thank you on behalf of your appreciated Guidance.

## CONCLUSION:

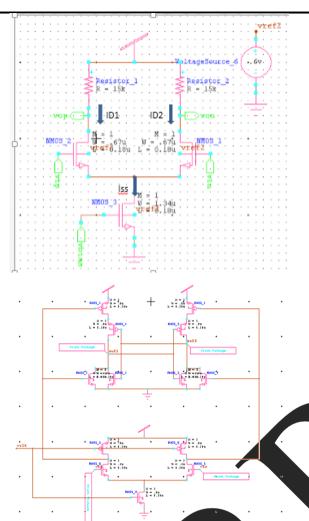

The FLASH Analog to Digital converter architecture is the good solution for high Speed Analog to Digital converter Design. To achieve Power and Speed trade of we used Dynamic latch Comparator along with multiplexer and interpolation technique to reduce comparator count. Design is done in 180nm Tanner Tool, power Consumption for this circuit is  $2.3 \times 10^{-4}$ w and delay is 3.4us which is very less. So low power and high speed operation achieved

## **REFERENCES:**

- P.E Allen and D.R Hollberg. CMOS Analog Circuit Design Second Edition Oxford university press. ISBN 019 5116 445, 2002.

- Manju Devi,Arunkumar P Chavan,Dr. K.N.Murlidhara "A 1.5v 3 bit ,500MS/s Low Power CMOS Flash ADC." IJECS.

- 3) Mikael Gustavsson, J. Jacob Wikner and Nianxiong Nick Tan, CMOS Data Converters for Communications, Kluwer Academic Publishers,2000.

- 4) Rudy van de Plassche, CMOS integrated analog-todigital and digital-to- analog converters, Kluwer Academic Publishers, Boston, 2003.

- 5) Project Report 2013 Yatish Lavania," *Low power Encoder and Comparator Design of 5-bit Flash ADC.*"

- 6) Yogendra Gupta, Lokesh Garg, Sarthak Khandelwal, Sanchit Gupta, Sandeep Saini *Designof low power and high speed multiplexer based Thermometer to Gray Encoder*.IEEE 2013.

- 7) L. Wen-Ta, H. Po-Hsiang, L. Yi-Zhen, and H. Yuh-Shyan, "A New Low Power Floor ADS Using Multiple-Selection Method," IEEE Conference on Electron Devices and Solid-State Circuits (EDSSC), pp.341-344,2007.

- M. O. Shaker, S. Gosh, and M. A. Bayoumi, "A 1-GS/s 6bit flash ADC in 90 nm CMOS," IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 144-147, 2009.

- 9) Ke Jong-In, K. Wan, S. Barosaim, and R. Beung-Tak, "*A time-domain latch interpolation technique for low power flash ADCs*." IEEE Custom Integrated Circuits Conference (CICC), pp. 114, 2011.